JK Flip-Flop

JK flip-flop merupakan flip flop yang dibangun berdasarkan pengembangan dari RS flip-flop. JK flip-flop sering diaplikasikan sebagai komponen dasar suatu counter atau pencacah naik (up counter) ataupun pencacah turun (down counter). JK flip flop dalam penyebutanya di dunia digital sering di tulis dengan simbol JK -FF. Dalam artikel yang sedikit ini akan diuraikan cara membangun sebuah JK flip-flop menggunakan komponen utama berupa RS flip-flop.

Rangkaian Dasar JK Flip-Flop

Gambar rangkaian diatas memperlihatkan salah satu cara untuk membangun sebuah flip-flop JK, J dan K disebut masukan pengendali karena menentukan apa yang dilakukan oleh flip-flop pada saat suatu pinggiran pulsa positif diberikan. Rangkaian RC mempunyai tetapan waktu yang sangat pendek, hal ini mengubah pulsa lonceng segiempat menjadi impuls sempit. Pada saat J dan K keduanya 0, Q tetap pada nilai terakhirnya.

Pada saat J rendah dan K tinggi, gerbang atas tertutup, maka tidak terdapat kemungkinan untuk mengeset flip-flop. Pada saat Q adalah tinggi, gerbang bawah melewatkan pemicu reset segera setelah pinggiran pulsa lonceng positif berikutnya tiba. Hal ini mendorong Q menjadi rendah . Oleh karenanya J = 0 dan K=1 berarti bahwa pinggiran pulsa lonceng positif berikutnya akan mereset flip-flopnya.

Pada saat J tinggi dan K rendah, gerbang bawah tertutup dan pada saat J dan K keduanya tinggi, kita dapat mengeset atau mereset flip-flopnya. Untuk lebih jelasnya daat dilihat pada tabel kebenaran JK flip-flop berikut.

Tabel Kebenaran JK Flip-Flop

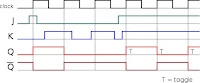

Selain dengan tabel kebenaran, dalam memahami karakteristik JK flip-flop seperti tabel diatas dapat dapat juga dipahami melalui timing diagram dari pemberian input kepada JK flip-flop seperti ditunjukan pada gambar berikut.

Timing Diagram JK Flip-Flop

Dari kedua penjelasan diatas (tabel kebenaran dan timing diagram) karakteristik JK flip-flop dapat kita pahami dengan cepat dan baik. Aplikasi JK flip-flop sering digunakan sebagai komponen utama suatu pencacah digital.